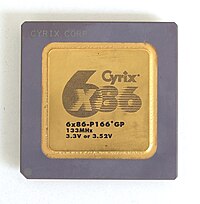

A Cyrix 6x86-P166 processor | |

| General information | |

|---|---|

| Launched |

|

| Discontinued |

|

| Marketed by | |

| Common manufacturers | |

| Performance | |

| Max. CPU clock rate | 80 MHz to 333 MHz |

| FSB speeds | 40 MHz to 100 MHz |

| Cache | |

| L1 cache |

|

| Architecture and classification | |

| Application | Desktop |

| Microarchitecture | 6x86 |

| Instruction set | x86-16, IA-32 |

| Physical specifications | |

| Transistors |

|

| Cores |

|

| Sockets | |

| Products, models, variants | |

| Core names |

|

| Variant |

|

| History | |

| Predecessor | Cyrix 5x86 |

| Successor | Cyrix III |

The Cyrix 6x86 is a line of sixth-generation, 32-bit x86 microprocessors designed and released by Cyrix in 1995. Cyrix, being a fabless company, had the chips manufactured by IBM and SGS-Thomson.[1][2] The 6x86 was made as a direct competitor to Intel's Pentium microprocessor line, and was pin compatible. During the 6x86's development, the majority of applications (office software as well as games) performed almost entirely integer operations. The designers foresaw that future applications would most likely maintain this instruction focus. So, to optimize the chip's performance for what they believed to be the most likely application of the CPU, the integer execution resources received most of the transistor budget. This would later prove to be a strategic mistake, as the popularity of the P5 Pentium caused many software developers to hand-optimize code in assembly language, to take advantage of the P5 Pentium's tightly pipelined and lower latency FPU. For example, the highly anticipated first-person shooter Quake used highly optimized assembly code designed almost entirely around the P5 Pentium's FPU. As a result, the P5 Pentium significantly outperformed other CPUs in the game.[3][4][5][6]

- ^ Slater, Michael (May 28, 1996). "Beyond the Pentium; Intel's top challengers have reached the Pentium level, but do they pose a threat to the king of the CPU hill? We examine the chips and vendors to find out". PC Mag. Vol. 15, no. 10. Ziff Davis, Inc. pp. 100–102. ISSN 0888-8507. Retrieved March 30, 2022.

- ^ "CYRIX CLAIMS ITS 100MHZ 6X86 CLONE IS THE FASTEST". TechMonitor. October 9, 1995. Retrieved April 25, 2022.

- ^ Potoroaca, Adrian (December 30, 2021). "Cyrix: Gone But Not Forgotten; Peak Cyrix Through the Lens of Quake". TechSpot. Retrieved April 5, 2022.

- ^ Proven, Liam (June 5, 2016). "The rise & fall of the first real x86 rival to Intel: the Cyrix 6x86". Liam On Linux. Archived from the original on April 22, 2021. Retrieved April 5, 2022.

- ^ Shimpi, Anand (April 8, 1997). "Cyrix 6x86 MX". AnandTech. Retrieved April 7, 2022.

- ^ Sood, Yatharth (July 24, 2020). "How did a single game lead to the shake-up of an entire industry, and sounded the death knell of an entire corporation?". Medium. Retrieved April 7, 2022.