This article needs additional citations for verification. (November 2015) |

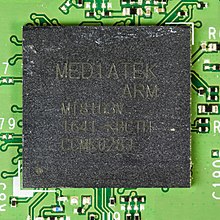

A picture of the Amazon Echo Dot (RS03QR) - motherboard | |

| General information | |

|---|---|

| Launched | 2012 |

| Designed by | ARM Holdings |

| Performance | |

| Max. CPU clock rate | 400 MHz to 2.30 GHz |

| FSB speeds | 100 MHz to 118 MHz OC |

| Cache | |

| L1 cache | 8–64 KiB |

| L2 cache | 128 KiB – 2 MiB |

| Architecture and classification | |

| Instruction set | ARMv8-A |

| Physical specifications | |

| Cores |

|

| Products, models, variants | |

| Product code name |

|

| History | |

| Predecessor | ARM Cortex-A7 |

| Successor | ARM Cortex-A55 |

The ARM Cortex-A53 is one of the first two central processing units implementing the ARMv8-A 64-bit instruction set designed by ARM Holdings' Cambridge design centre, along with the Cortex-A57. The Cortex-A53 is a 2-wide decode superscalar processor, capable of dual-issuing some instructions.[1] It was announced October 30, 2012[2] and is marketed by ARM as either a stand-alone, more energy-efficient alternative to the more powerful Cortex-A57 microarchitecture, or to be used alongside a more powerful microarchitecture in a big.LITTLE configuration. It is available as an IP core to licensees, like other ARM intellectual property and processor designs.

- ^ "Cortex-A53 Processor". ARM Holdings. Retrieved 2015-11-08.

- ^ "ARM Launches Cortex-A50 Series, the World's Most Energy-Efficient 64-bit Processors" (Press release). ARM Holdings. 2012-10-30. Retrieved 2023-05-15.